香港科技大学的研究人员最近发明了一种新型集成方案,透过选择性直接外延技术1,在硅光子平台上开发了III-V族化合物半导体器件和硅组件的高效耦合—,释放集成高能效光子和低成本电子的潜能,令下一代通信 可以低成本、更高速和更大容量的方式呈现。

近年,在大数据、汽车、云端和传感器等各种应用和新兴技术的推动下,数据流量呈指数级增长。为了解决数据通信的瓶颈,硅光子学成为一项被广泛研究的核心技术,通过节能、大容量和低成本的光互连实现数据传输的增长。虽然硅基无源组件已经在硅光子平台上成熟的建立,但激光器和光电探测器并不能由硅制成,需要在硅上集成其他材料,例如 III-V 族化合物半导体等。

现时对于硅上的 III-V 激光器和光电探测器主要通过两种方法进行了研究。第一个是以键合为基础的方法,尽管此方法已能产出了性能很好的器件,但要求复杂的制造工艺,而且成本高、产量低,使大规模生产变得非常具挑战性。另一种方法是通过在硅上纵向生长多层 III-V 的直接外延方法,虽然它提供了一种成本更低、可扩展性更大和集成密度更高的解决方案,然而这种方法中所必须用到的几微米厚的 III-V 缓冲层阻碍了 III-V 和硅之间的有效光耦合,因此解决这一问题成为了集成硅光子学的关键。

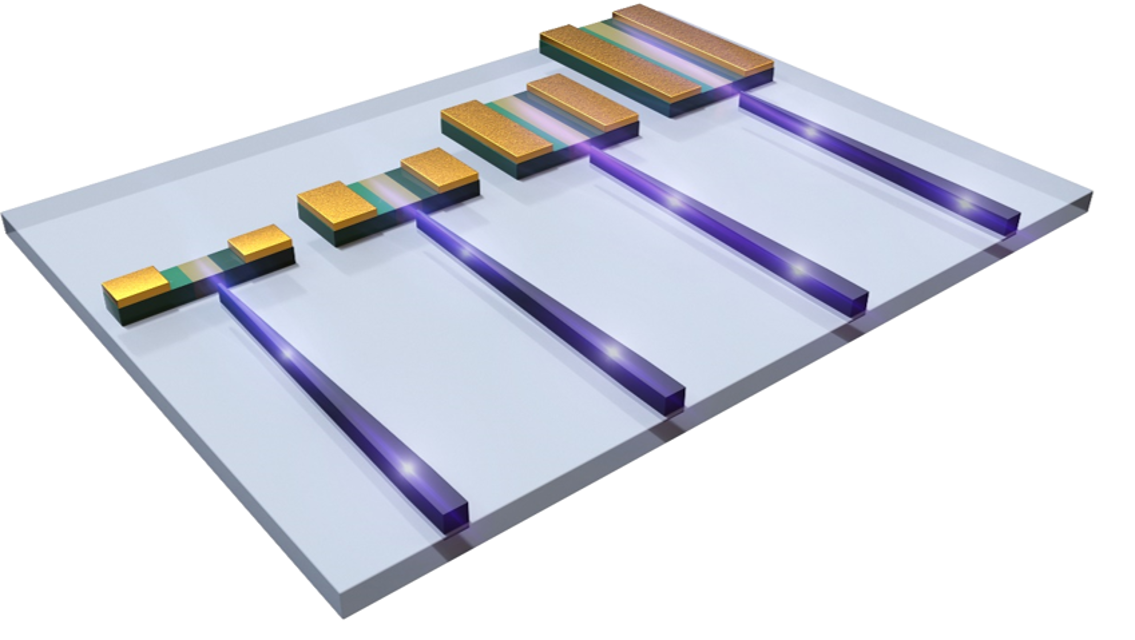

为解决这一关键问题,由香港科技大学电子及计算器工程学系荣休教授刘纪美领导的团队开发了横向选区生长技术—一种新颖的选择性直接外延方法,可以选择性地在硅上横向生长 III-V 材料,而无需缓冲层。此外,基于这项新技术,该团队亦设计并实现了 III-V 光电探测器和硅组件的独特面内集成,并在 III-V 和硅之间具有高耦合效率。与商用光电探测器相比,这种方法实现的光电探测器噪声更小,灵敏度更高,工作范围更广,且具有超过 112 Gb/s的高速—较现有产品更快。这不但乃首次通过直接外延的方法实现III-V 器件与硅组件的有效耦合,而且可以应用于各种 III-V 器件和硅基组件的集成,从而实现在硅光子平台上集成光与电模块以进行数据通信的最终目标。

刘教授表示:「我们开发的一种名为横向选区生长的新型技术以及我们在 SOI 平台上独特的耦合方案设计,令上述目标得以达成。我们的团队在器件物理和材料生长方面的专业知识和见解使我们能够完成 III-V 和硅之间有效耦合,让我们能完成外延生长和器件性能相关分析这个具挑战性任务。」

研究的第一作者薛莹博士指出: 「此项研究将为光集成电路和全集成硅光子提供可行的解决方案,运用此项研究技术,最具挑战的激光器与硅组件的有效耦合将有可能在未来实现」。

这项研究计划是与香港中文大学电子工程学系曾汉奇教授和中山大学电子与信息工程学院蔡鑫伦教授所领导的研究团队共同合作完成。计划所使用的器件制备由科大清水湾校区的纳米系统制造实验中心所开发。这计划得到香港研究资助局和香港创新科技基金的支持并于最近发表在 《光学(Optica)》上。

1 外延是指一种于半导体器件制造过程中,在原有芯片上生长出新结晶以制成新半导体层的技术。